3EC/3NC 各種ソフトウェアインストールマニュアル

最終更新日: 2026/02/27

組込みプログラミング

この実験では、AMD社のFPGA向け回路設計ソフト「AMD Vivado™ Design Suite」を使用する。

実験前までに下記手順を全て終わらせてくること。

Vivadoのインストール

-

AMD XILINXのサイト にアクセスする。

-

2025.2を選択し開く。

ダウンロードページ バージョン選択画面 -

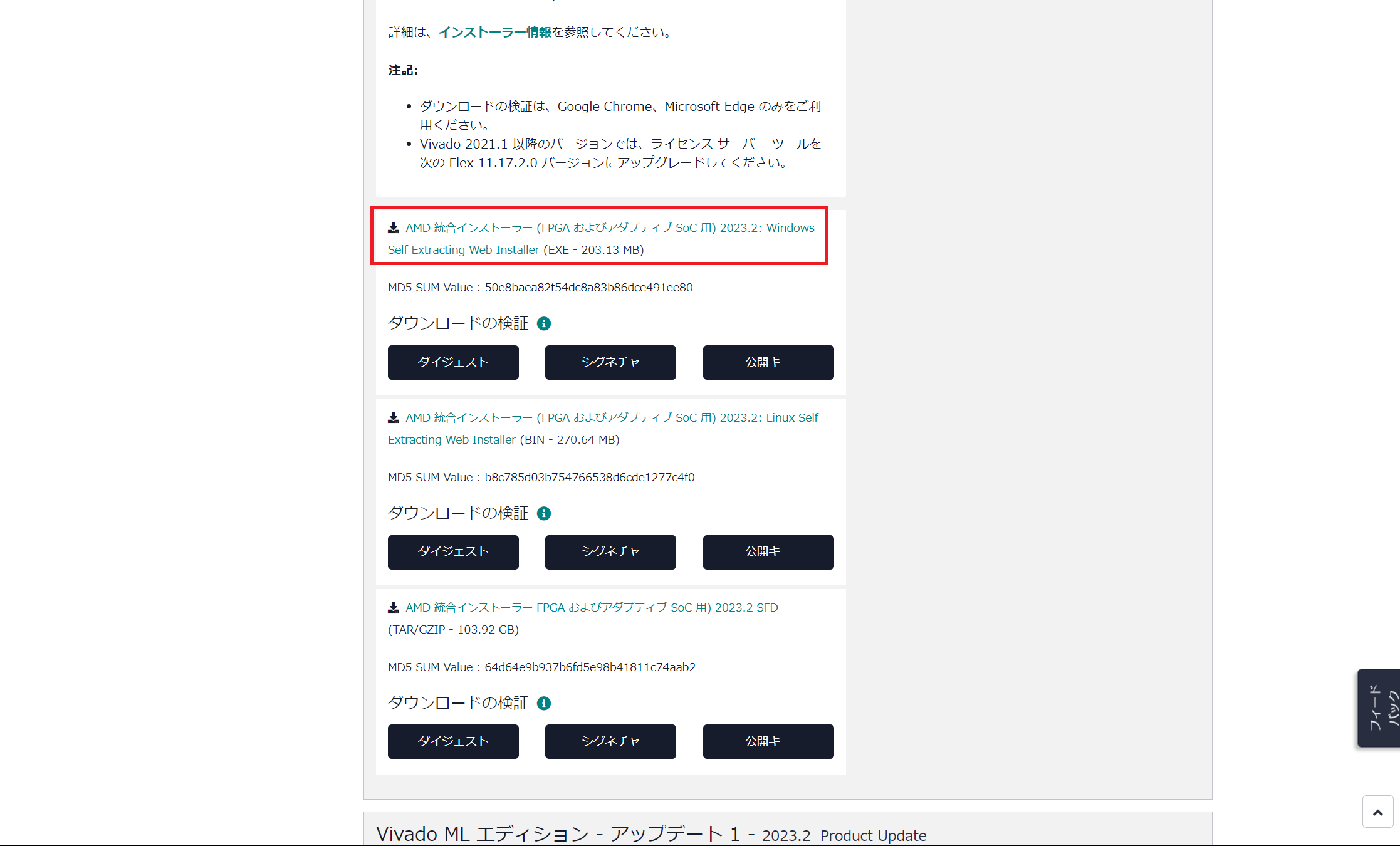

「AMD Unified Installer for FPGAs & Adaptive SoCs 2025.2: Windows Self Extracting Web Installer (EXE - 233.33 MB)」 をクリックする。

インストーラー選択画面 -

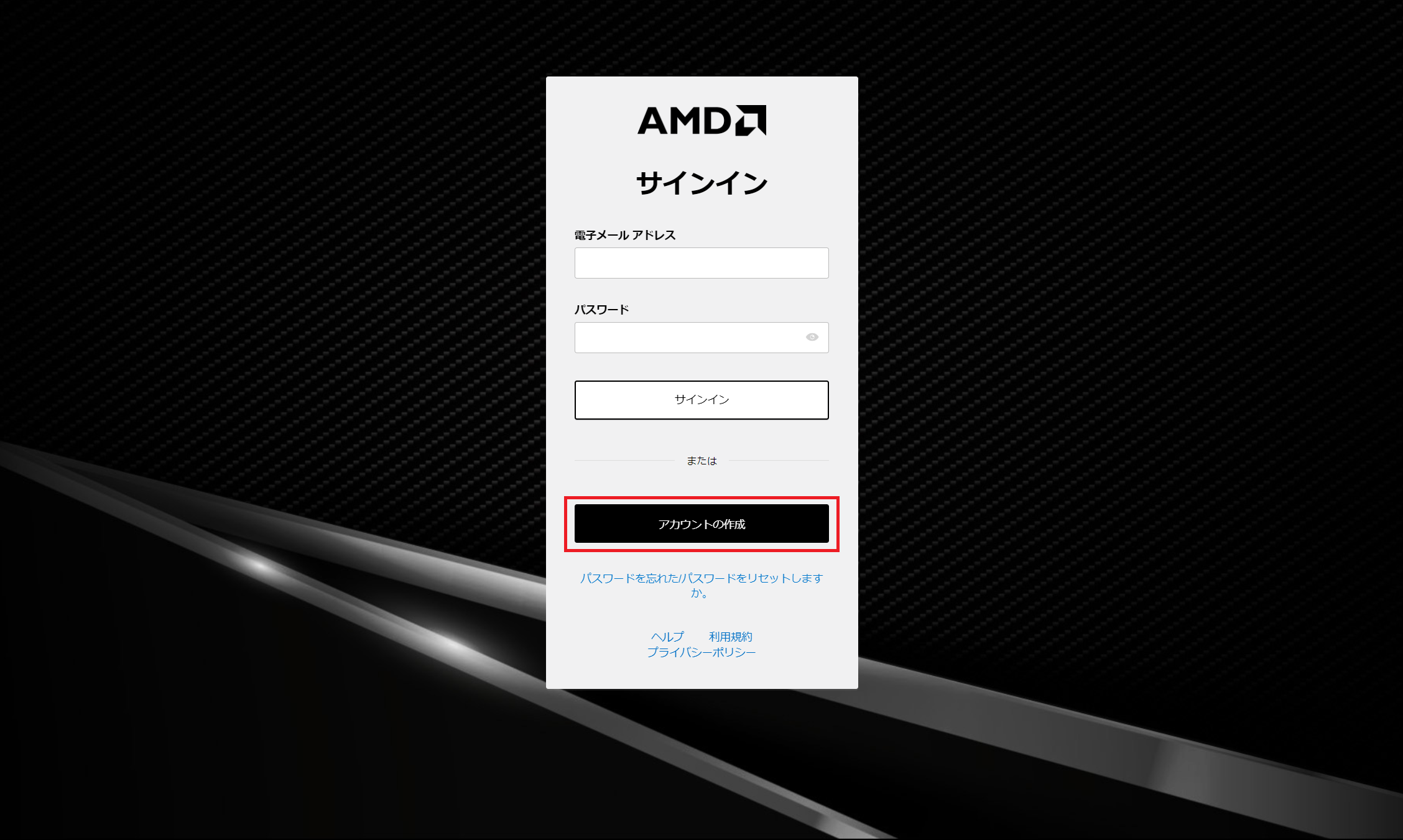

「アカウントの作成」をクリックする。

アカウント作成 画面 その1 -

以下に示す画像の赤枠内を入力してAMDアカウントを作成する。

アカウント選択 画面 その2 -

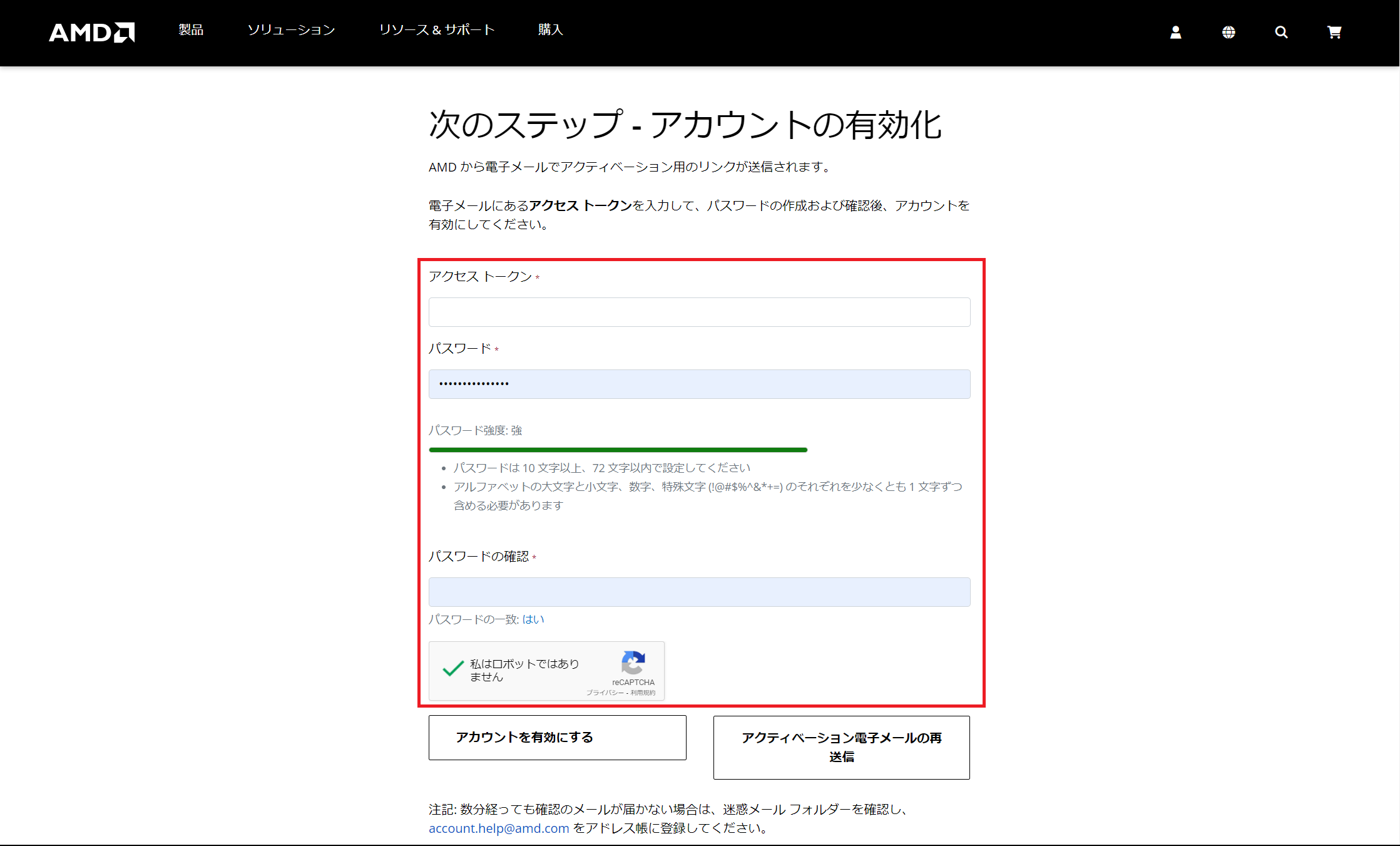

登録したメールアドレスに送られてきたアクセストークンを入力し、パスワードを設定して「アカウントを有効にする」をクリックする。

アカウントの有効化 -

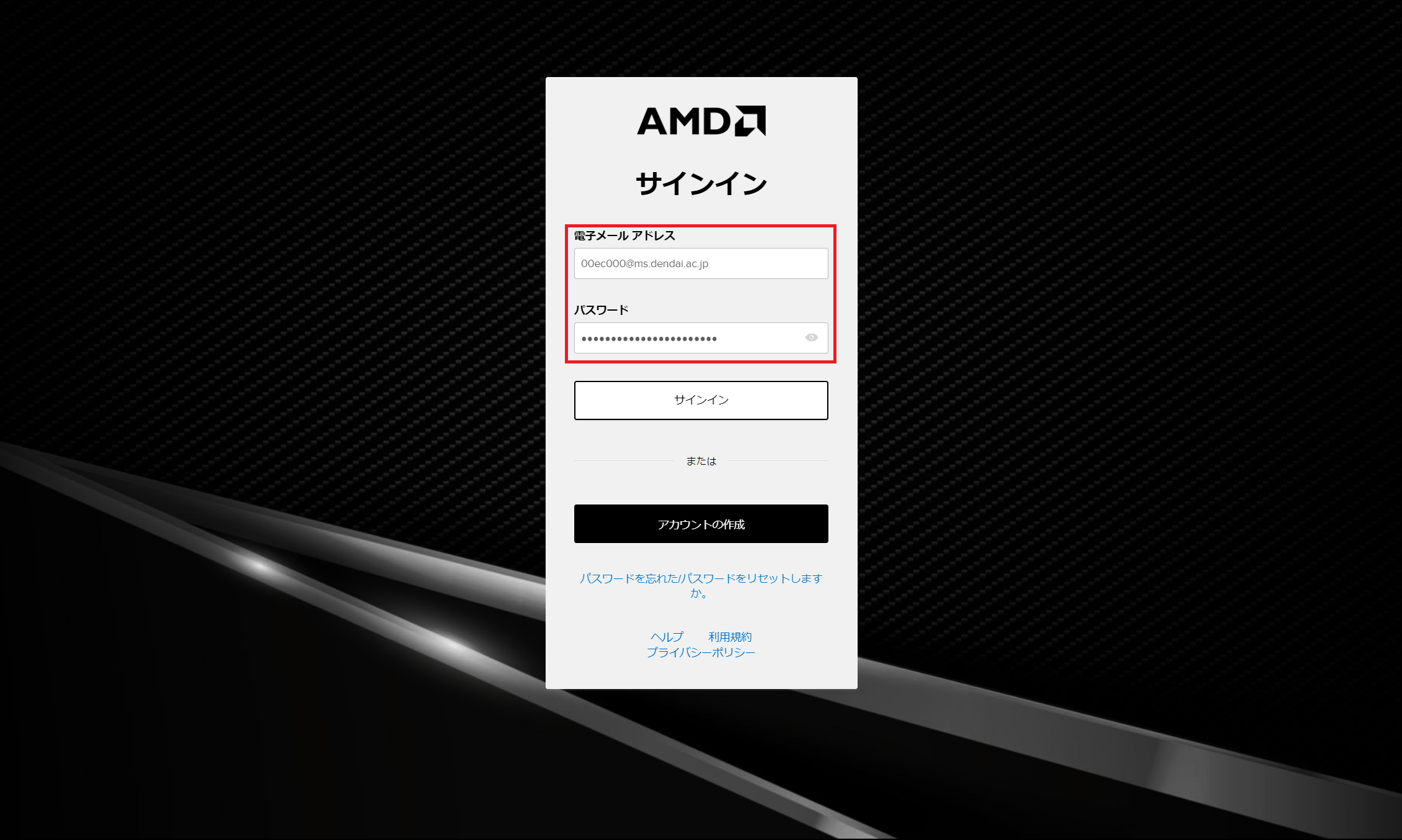

作成したAMDアカウントでサインインする。

サインイン -

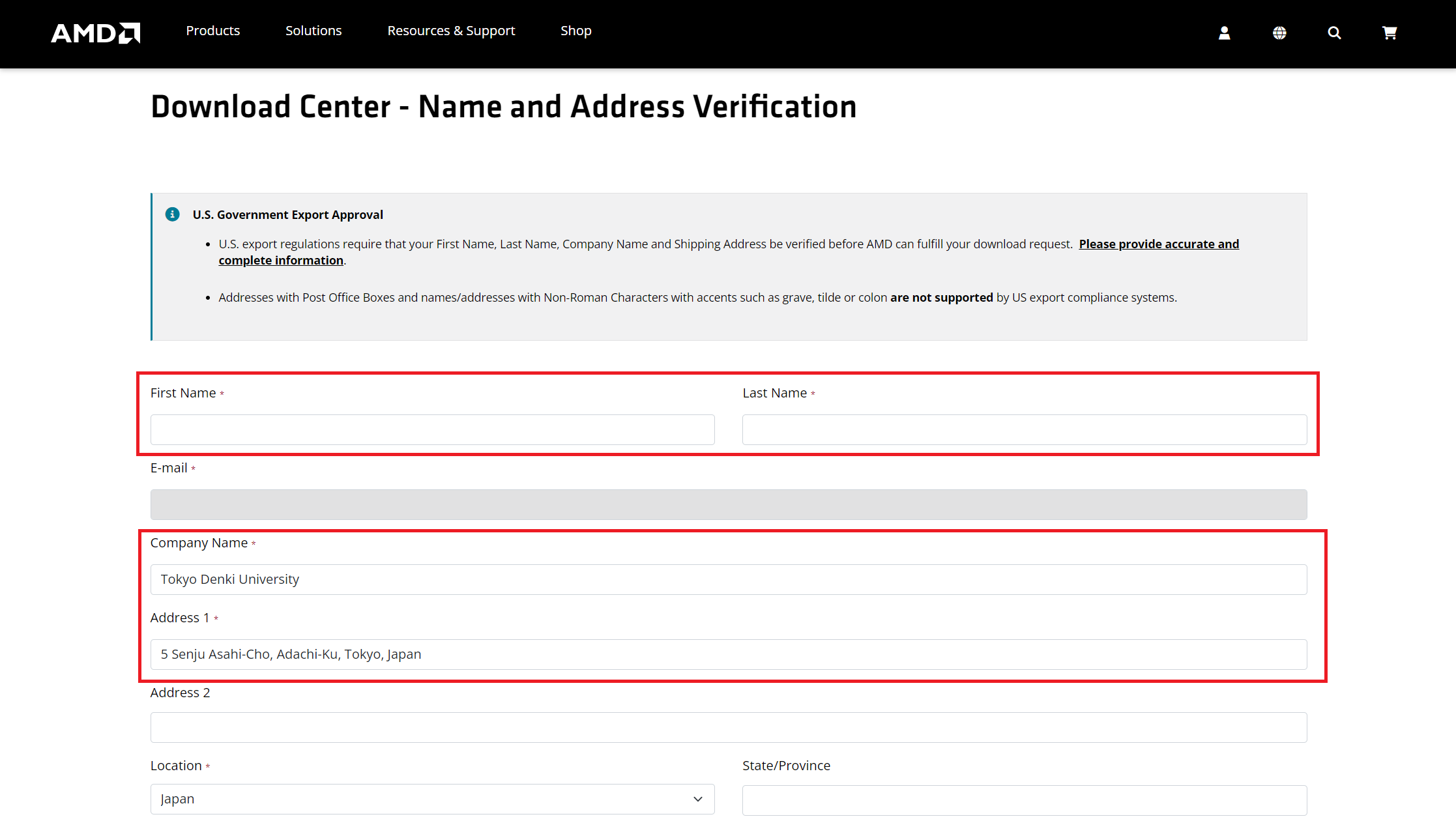

以下に示す画像の赤枠内を入力してダウンロードを開始する。 入力内容は以下の通り。

- First Name: 名前

- Last Name: 苗字

- Company Name: Tokyo Denki University

- Address1: 5 Senju Asahi-Cho, Adachi-Ku, Tokyo, Japan

- City: Adachi-Ku

- Job Function: Student

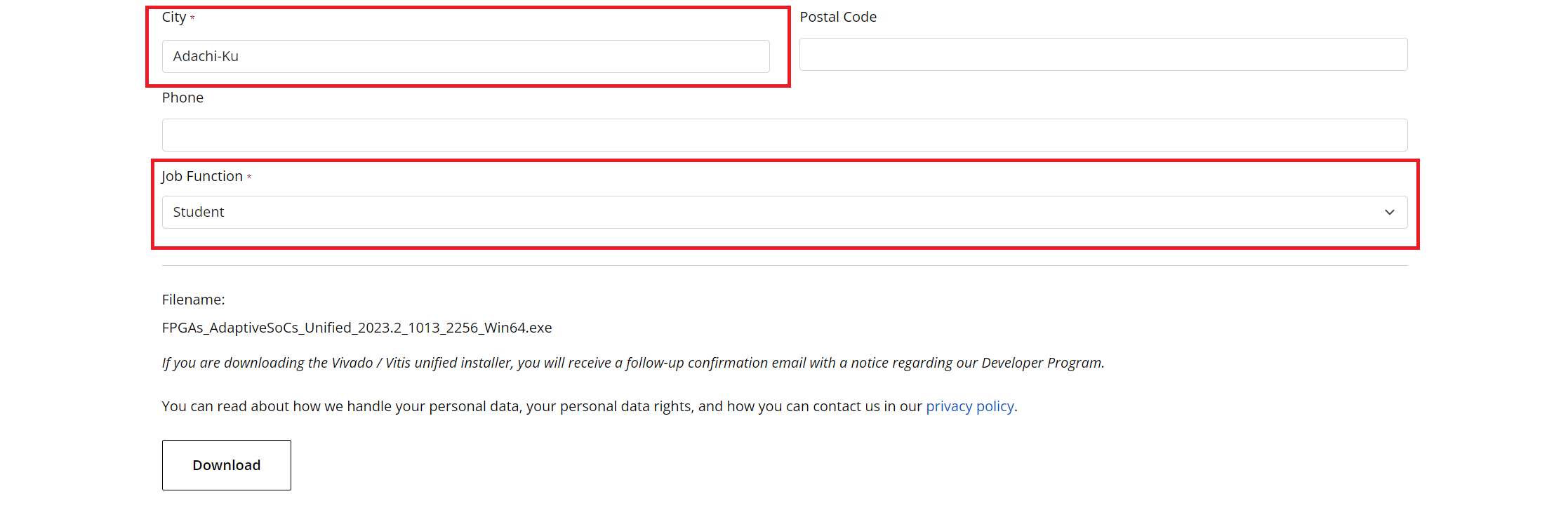

情報登録画面 その1

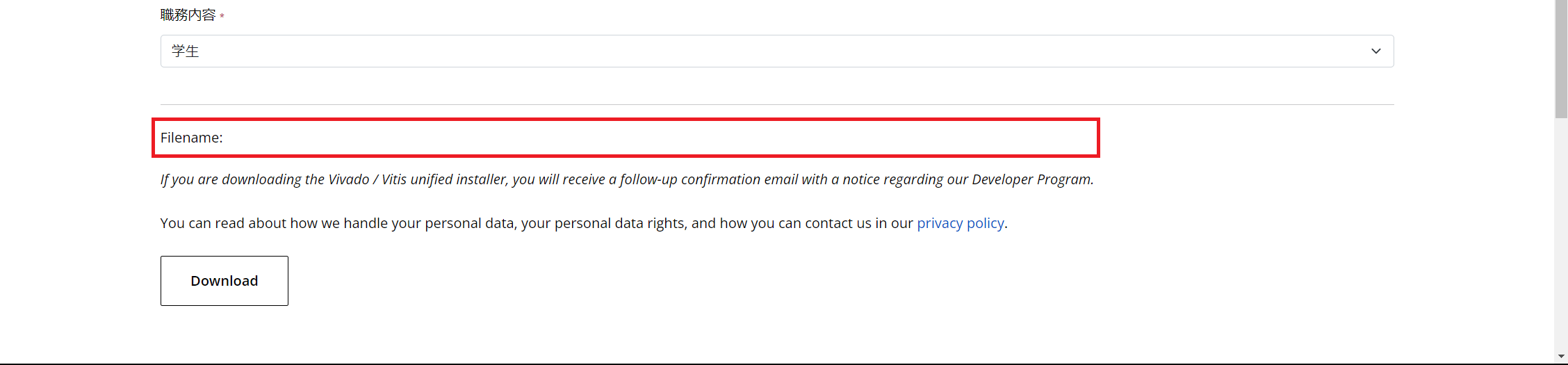

情報登録画面 その2 注意!

この画面で言語設定を変更した際や入力情報が不足していた際に画面が更新されると、Filenameが消えてしまい進めなくなってしまう。 その場合には、手順3からやり直すこと。

やり直し画面 -

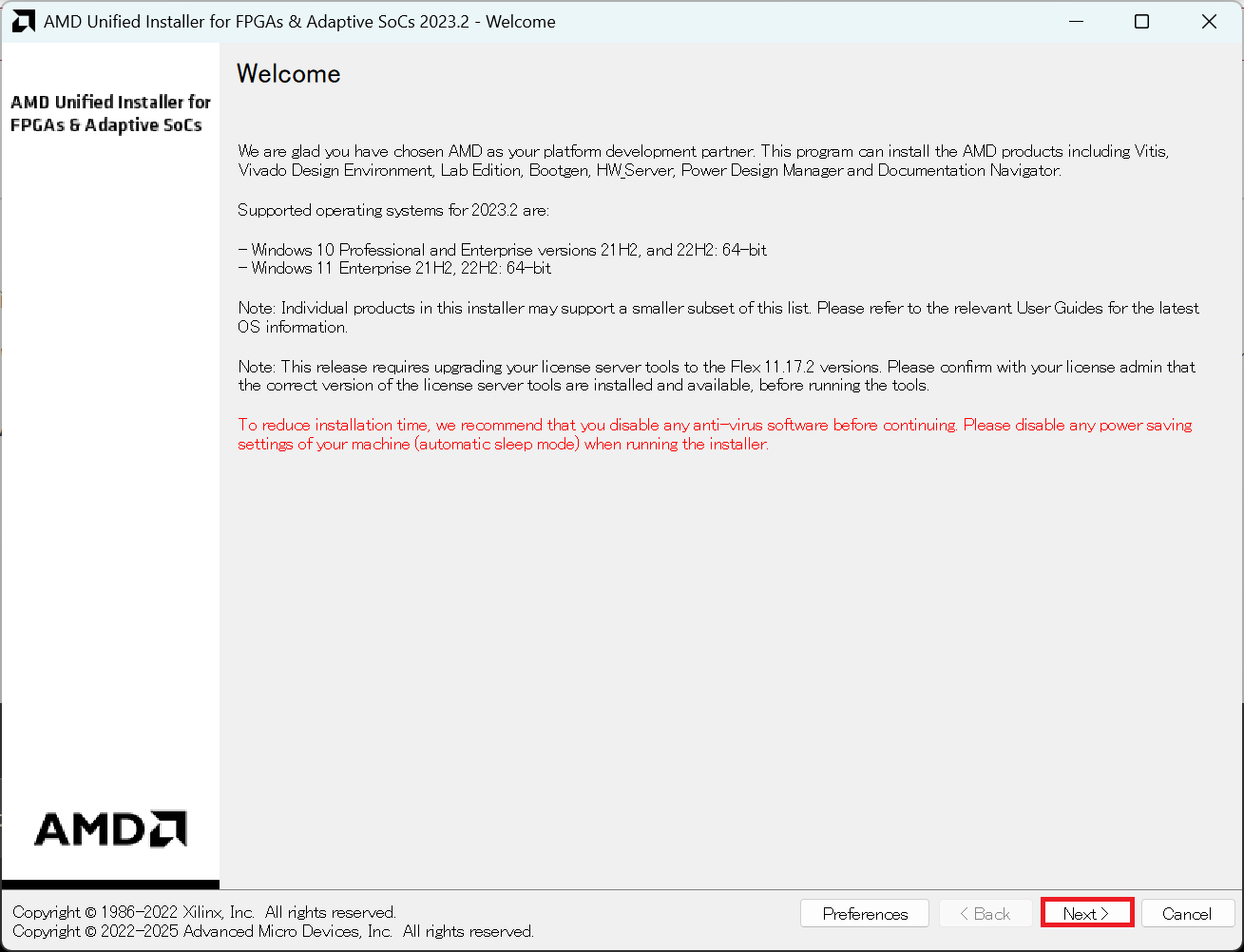

「Next」をクリックする。

Welcome -

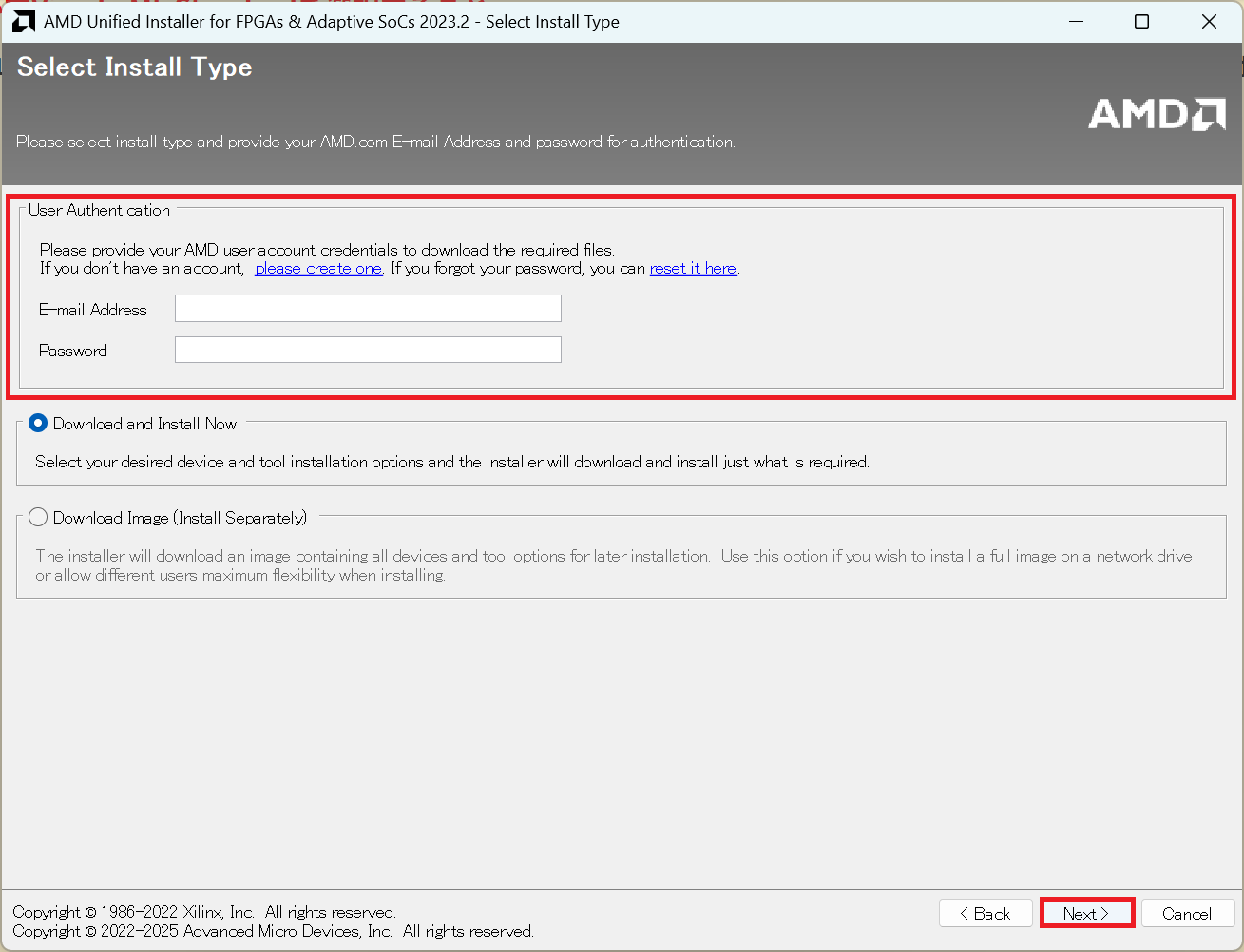

Select Install Typeの画面でAMDアカウントのメールアドレスとパスワードを入力し、「Download and Install Now」を選択して「Next」をクリックする。

ユーザーのメールアドレス、パスワード入力画面 -

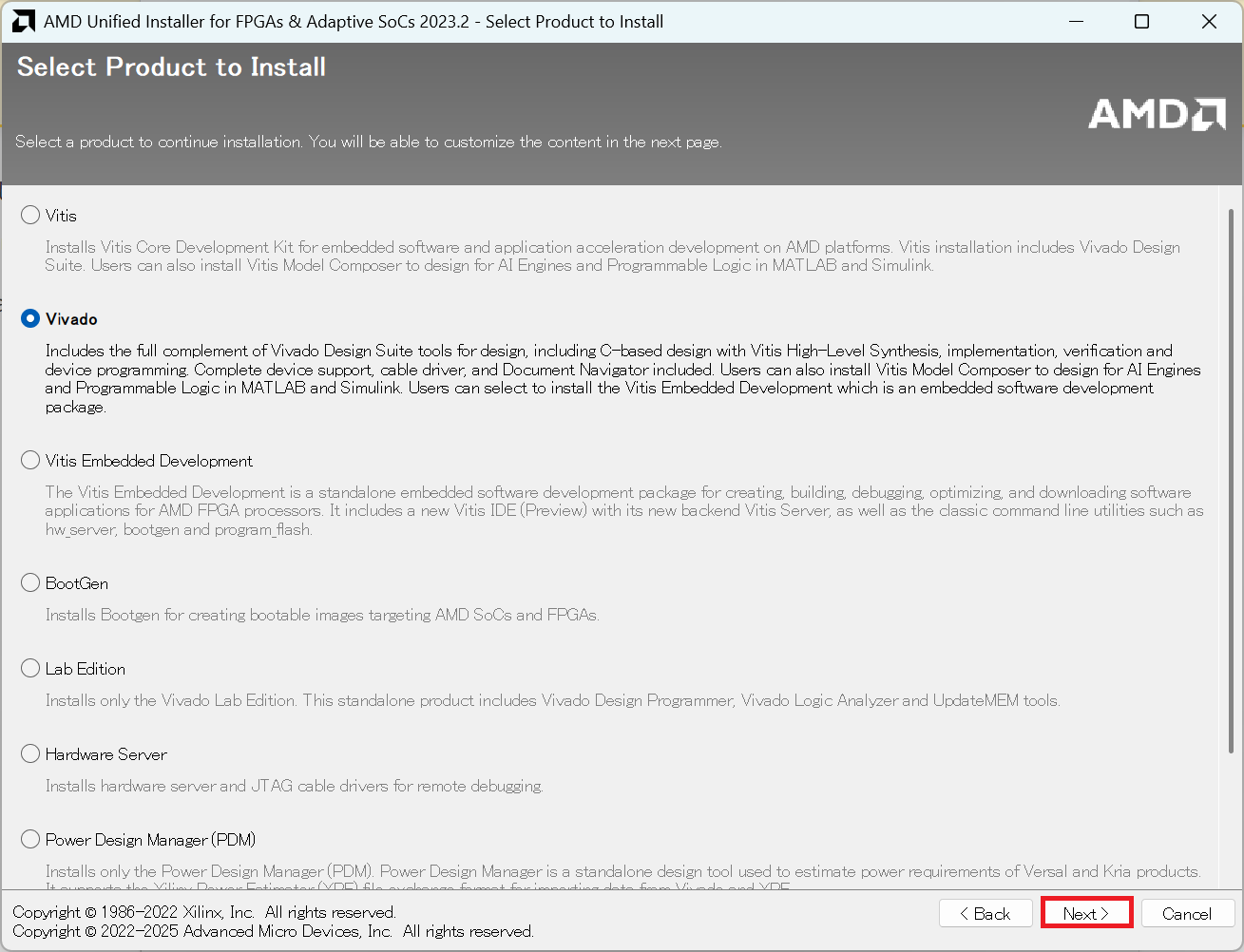

Vivadoを選択し、「Next」をクリックする。

Vivado 選択画面 -

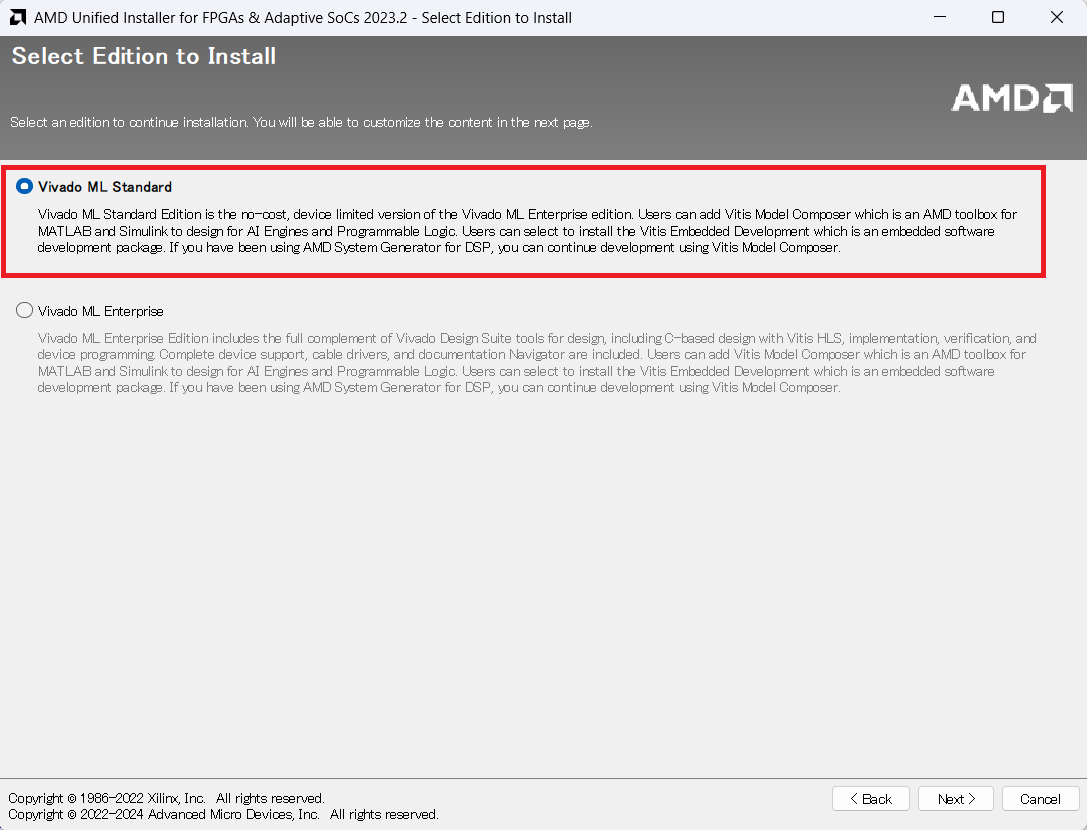

Select Edition to Installの画面で「Vivado ML Standard」を選択し、「Next」をクリックする。

インストールするエディションの選択 注意!必ずVivado ML Standardを選択すること

Vivado ML Standardは無償版であるので、必ずこちらを選択する。 Editionの指定ミスによる問い合わせが非常に多いので、気を付けて選択すること。

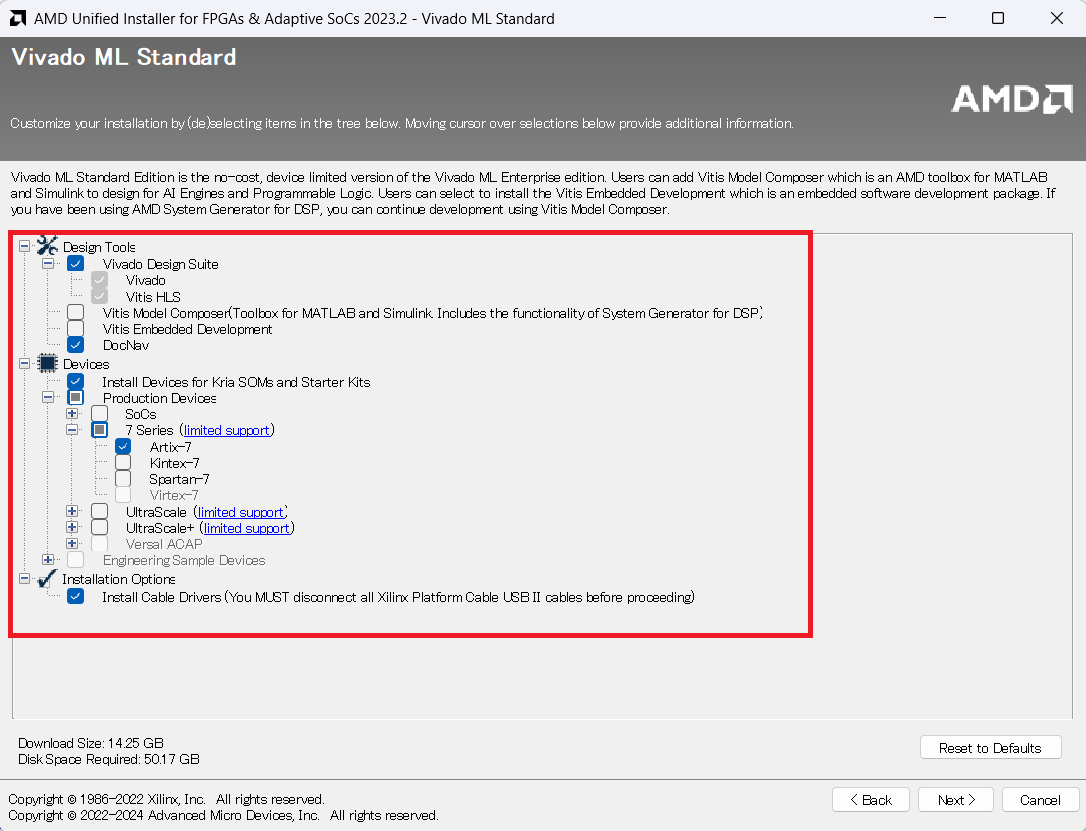

-

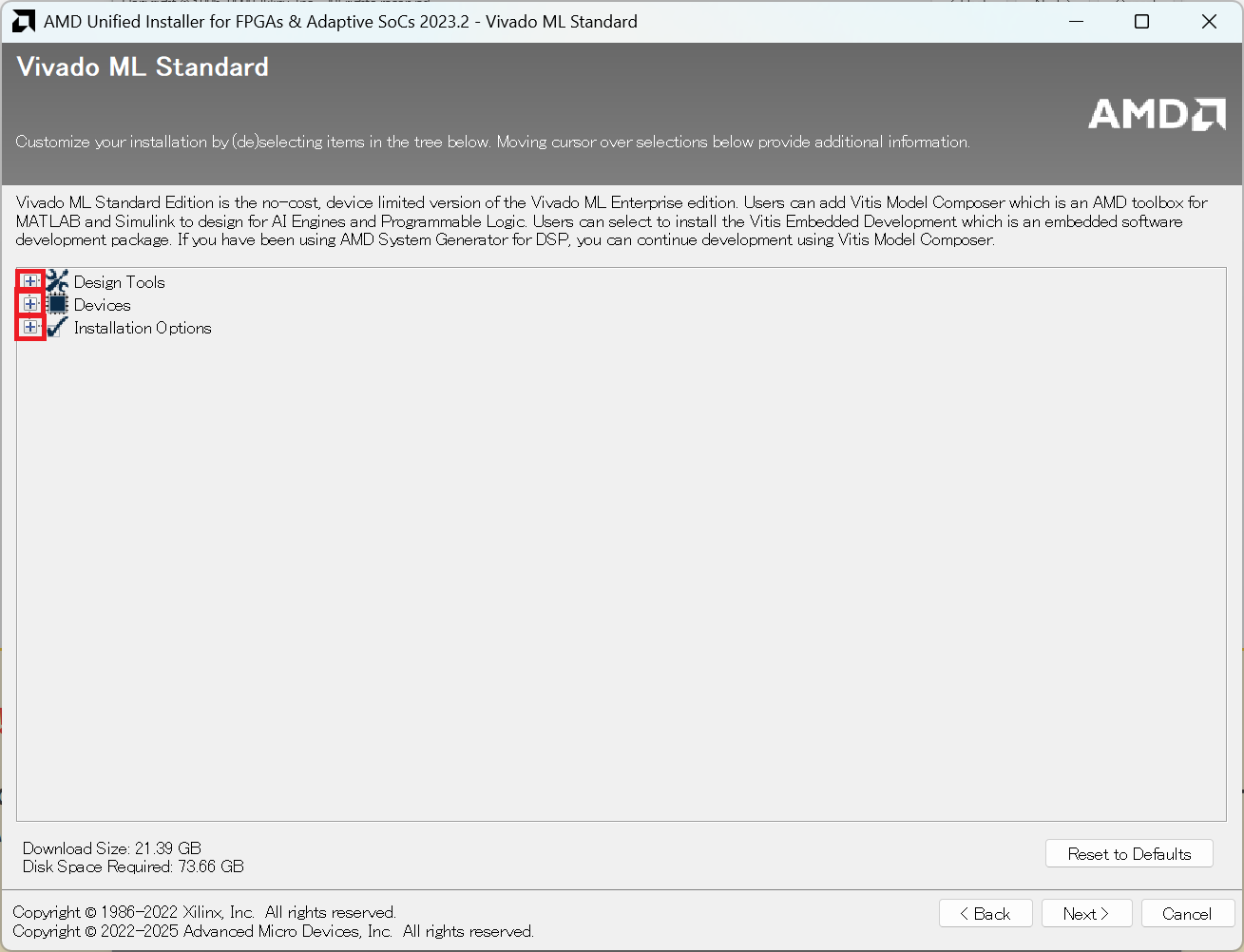

下の画面で赤枠に囲まれた+の部分をクリックし展開する。

Vivado ML Standard 選択画面 その1 展開したのちに以下に示す画像の通りにチェックを入れ、「Next」をクリックする。

Vivado ML Standard 選択画面 その2 注意!必ず画像の通りにチェックを入れること!

必要なチェックがないと実験で正しく動かない。 また、不要なチェックを入れるとダウンロードに必要な容量が無駄に増えてしまう。

-

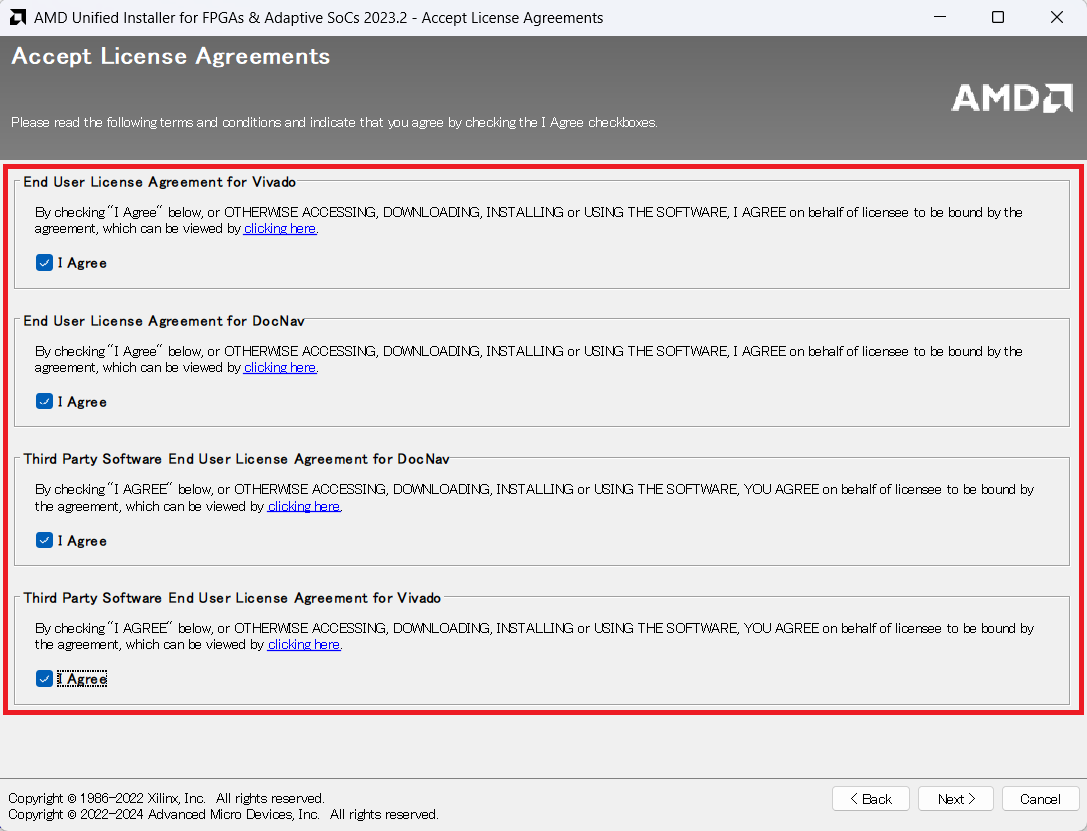

Accept License Agreementsの画面ですべて「I Agree」にチェックを入れ、「Next」をクリックする。 画面下にもチェックボックスがあるのでスクロールして下までみること。

同意 -

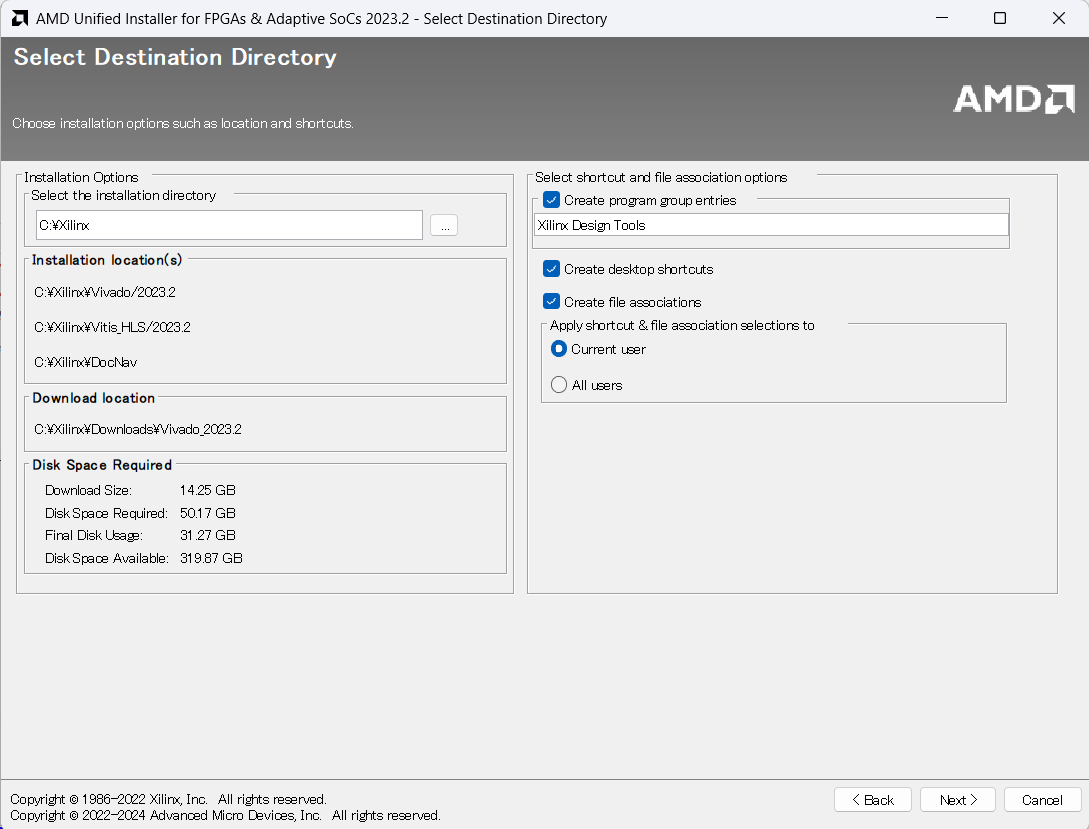

インストール場所の設定画面が開くので、そのまま「Next」を押す。(「All users」を選択してもよい)

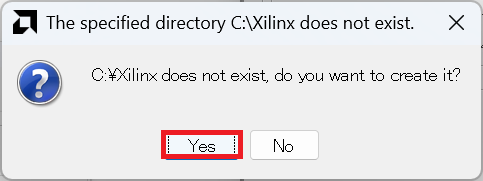

インストール場所の選択 ディレクトリが存在しない場合には警告が出るが、Yesを押し続行する。

警告画面 -

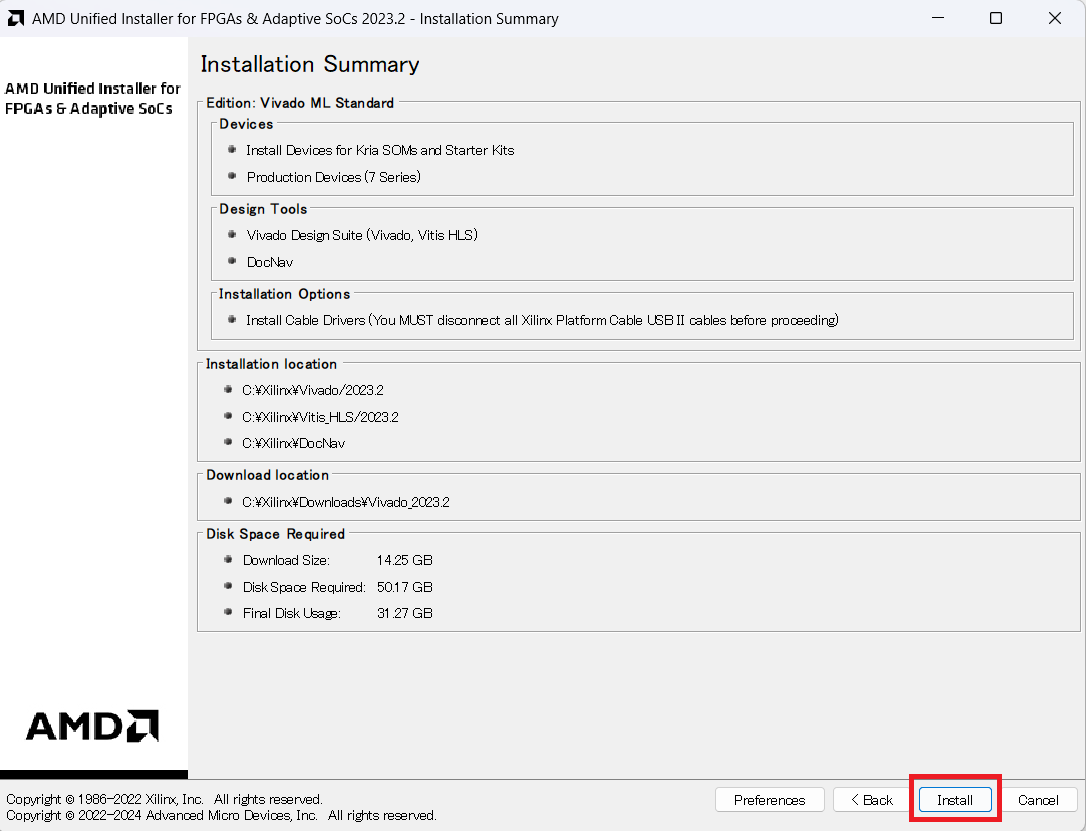

「Install」をクリックしてインストールを開始する。

インストール 確認画面 -

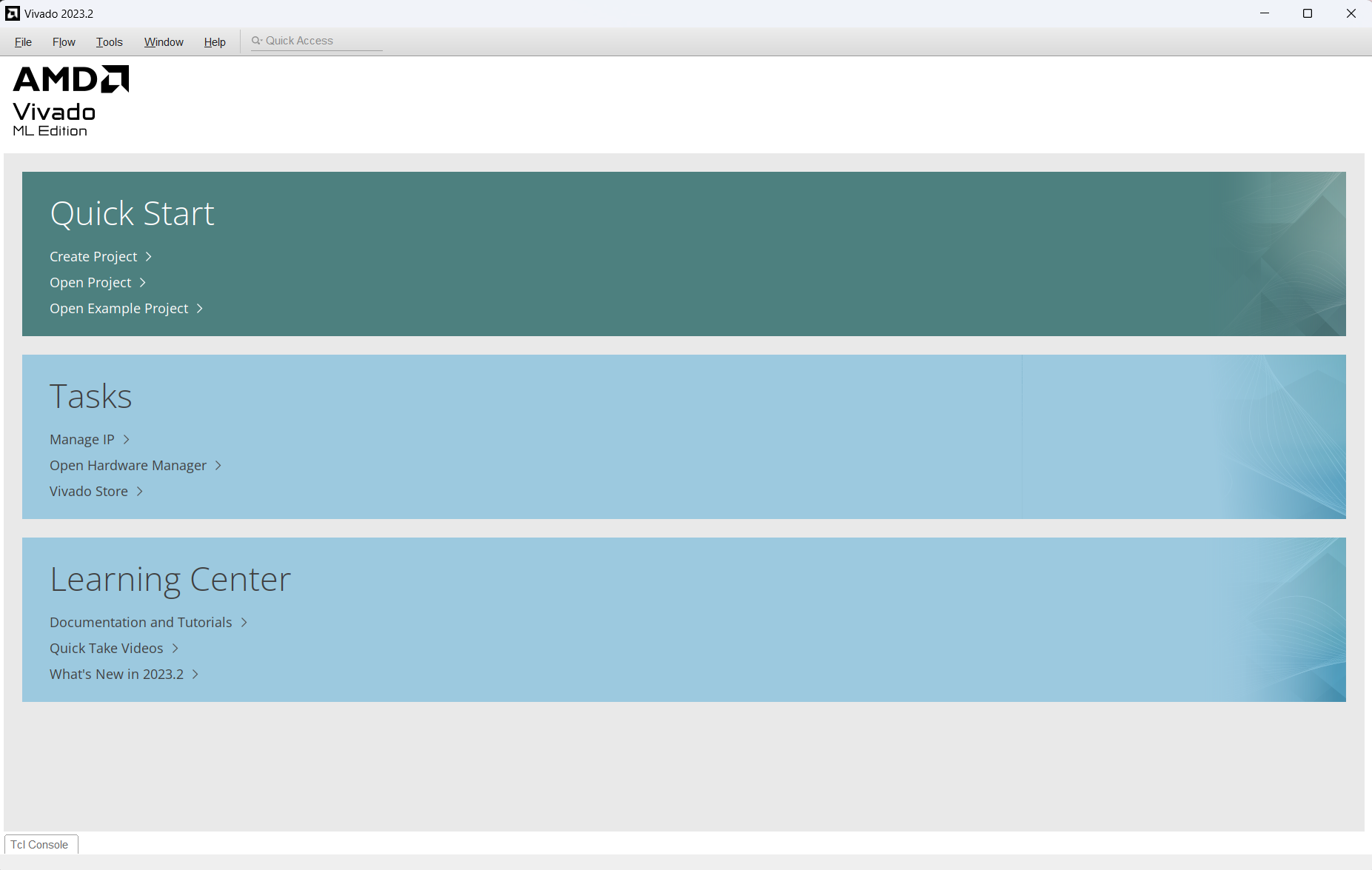

インストールが完了したらVivadoを起動し、以下の画面が出ればインストール成功である。

インストール完了画面

インストールができない際には

Vivadoを正常にインストールできない場合は、実験日より前に必ず1号館 5F 東京電機大学 情報通信工学科実験室 にメールもしくは直接訪問し問い合わせること。

動作確認

実験書記載の実験1「簡単プログラムFPGA1組込み開発の流れをつかもう」①~⑯を行う。

-

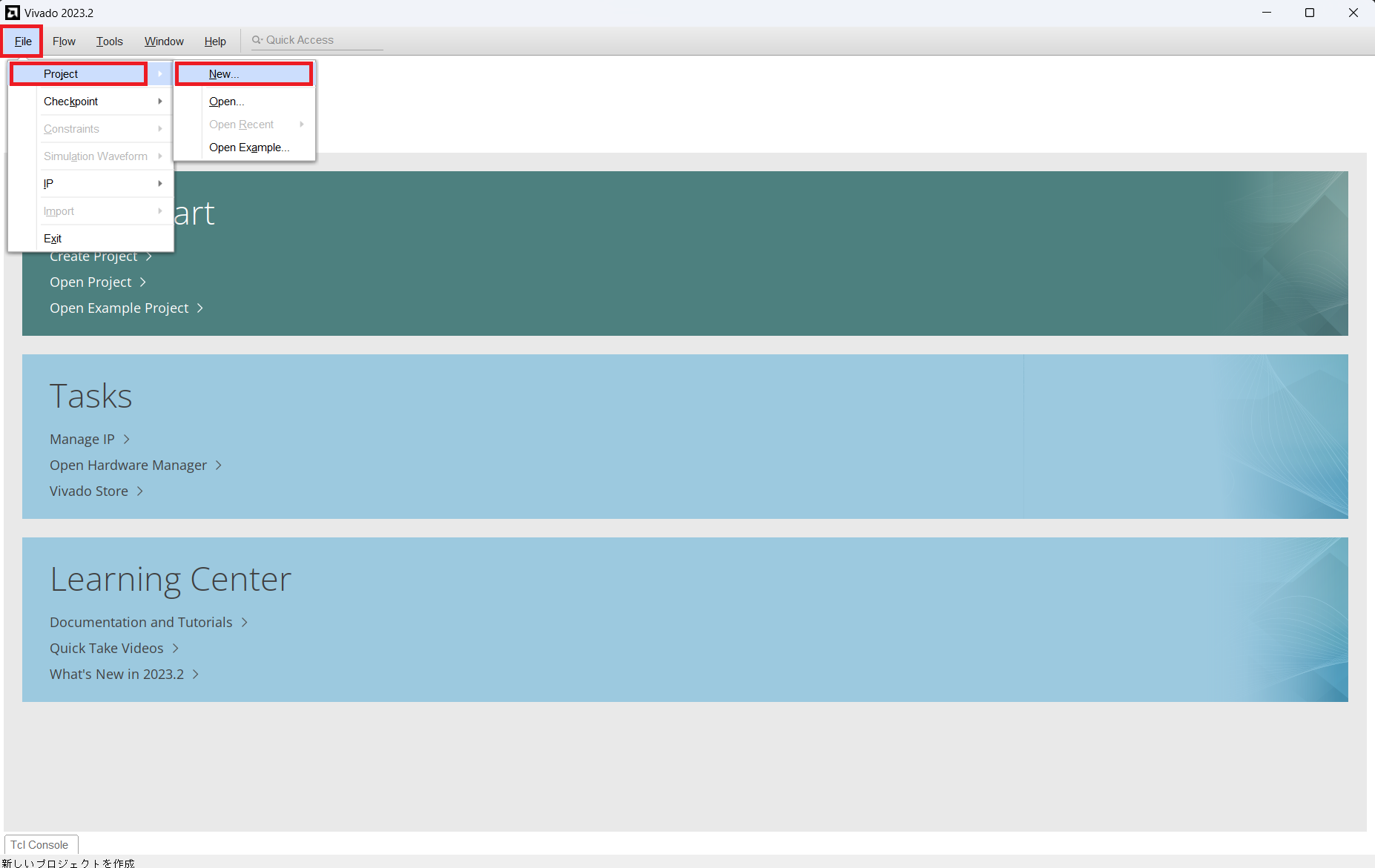

左上の「File」→「Project」→「New」を開き、Create a New Vivado Projectの画面で「Next」をクリックする。

Create a New Vivado Project その1 -

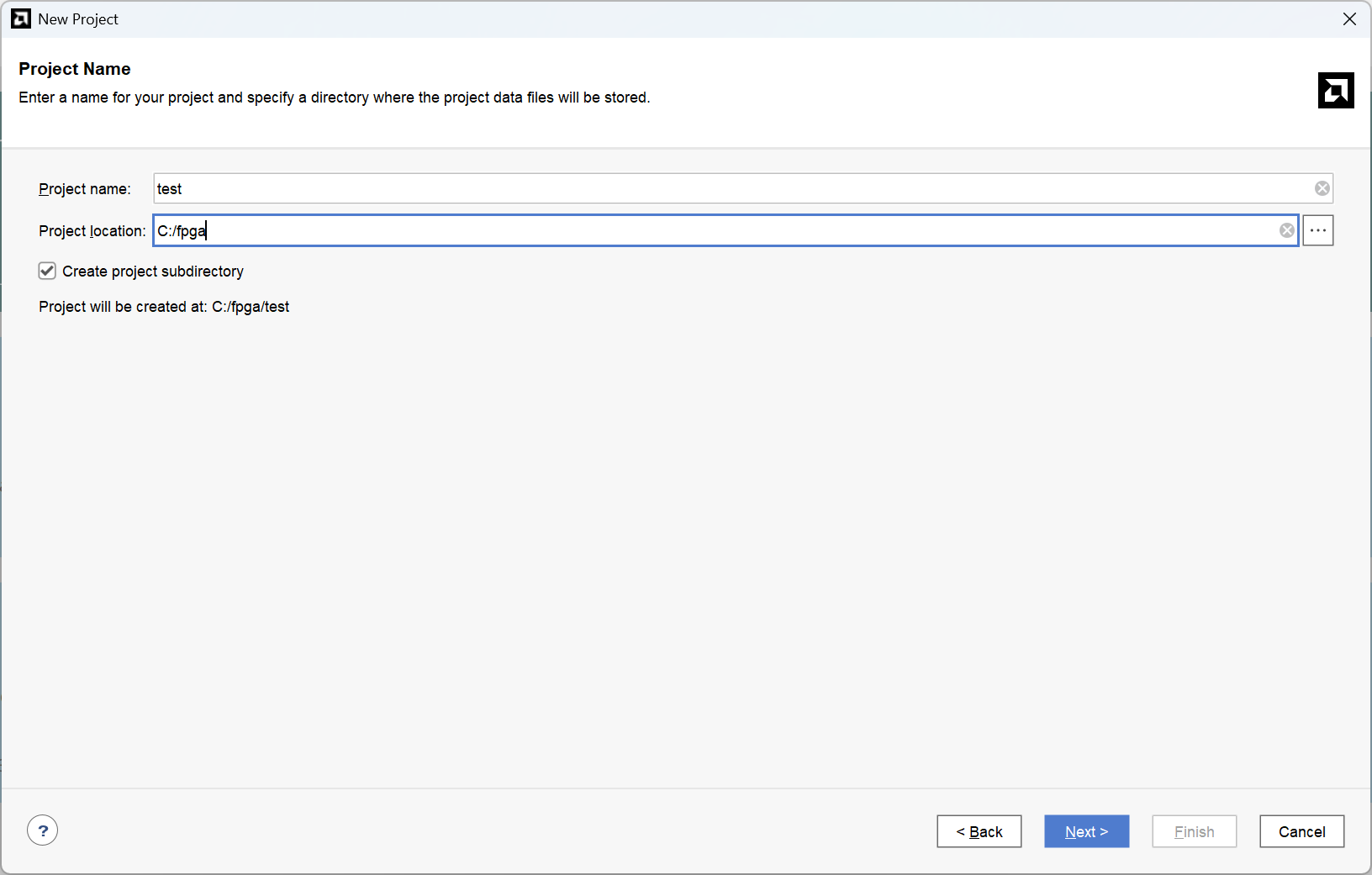

Project Nameの画面でプロジェクト名とプロジェクトの保存場所を設定し、「Next」をクリックする。

- Project name:test

- Project location:C:/fpga

保存場所は特に理由がない場合、変更しなくてよい。

Create a New Vivado Project その2 -

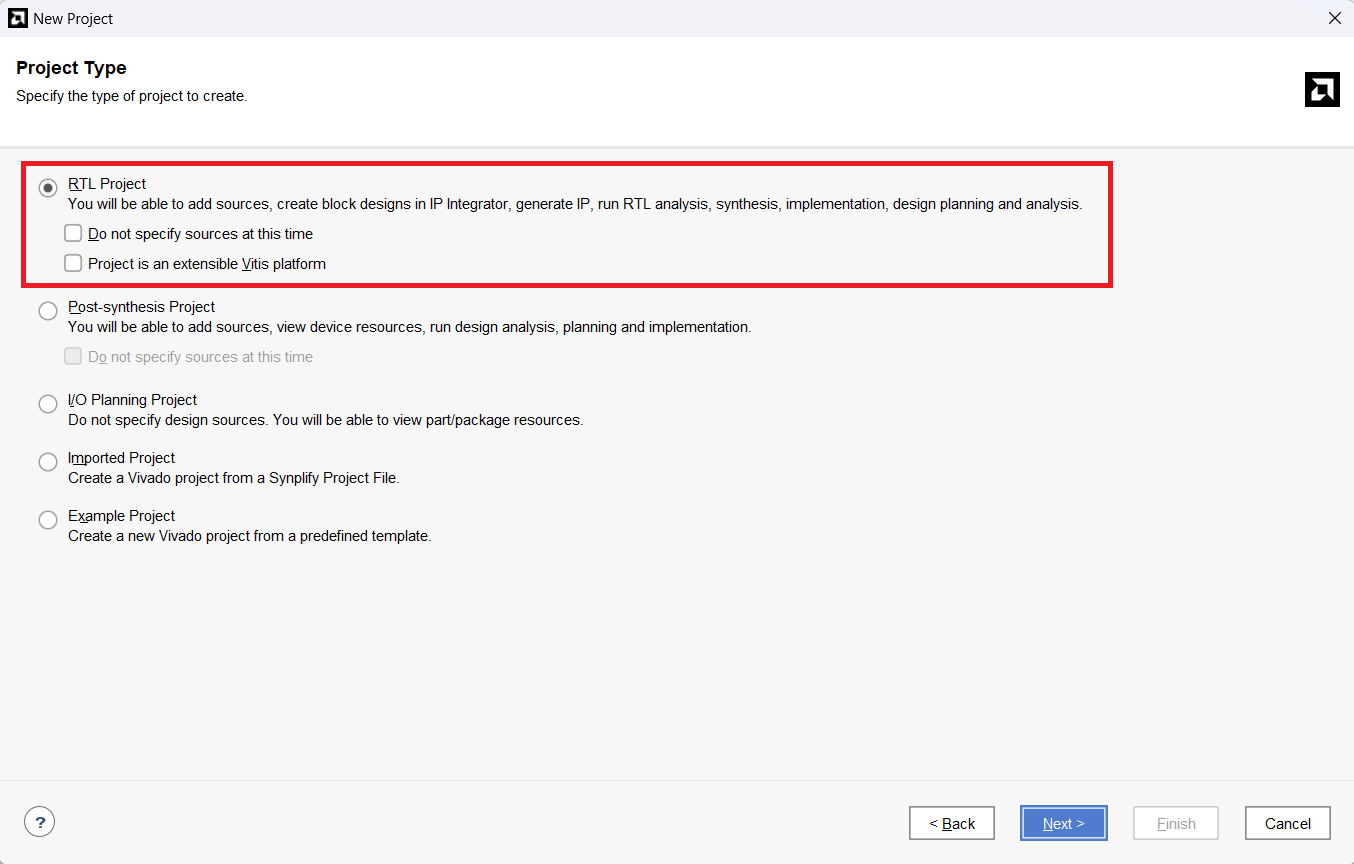

Project Typeの画面で「RTL Project」を選択し、「Next」をクリックする。

Create a New Vivado Project その3 -

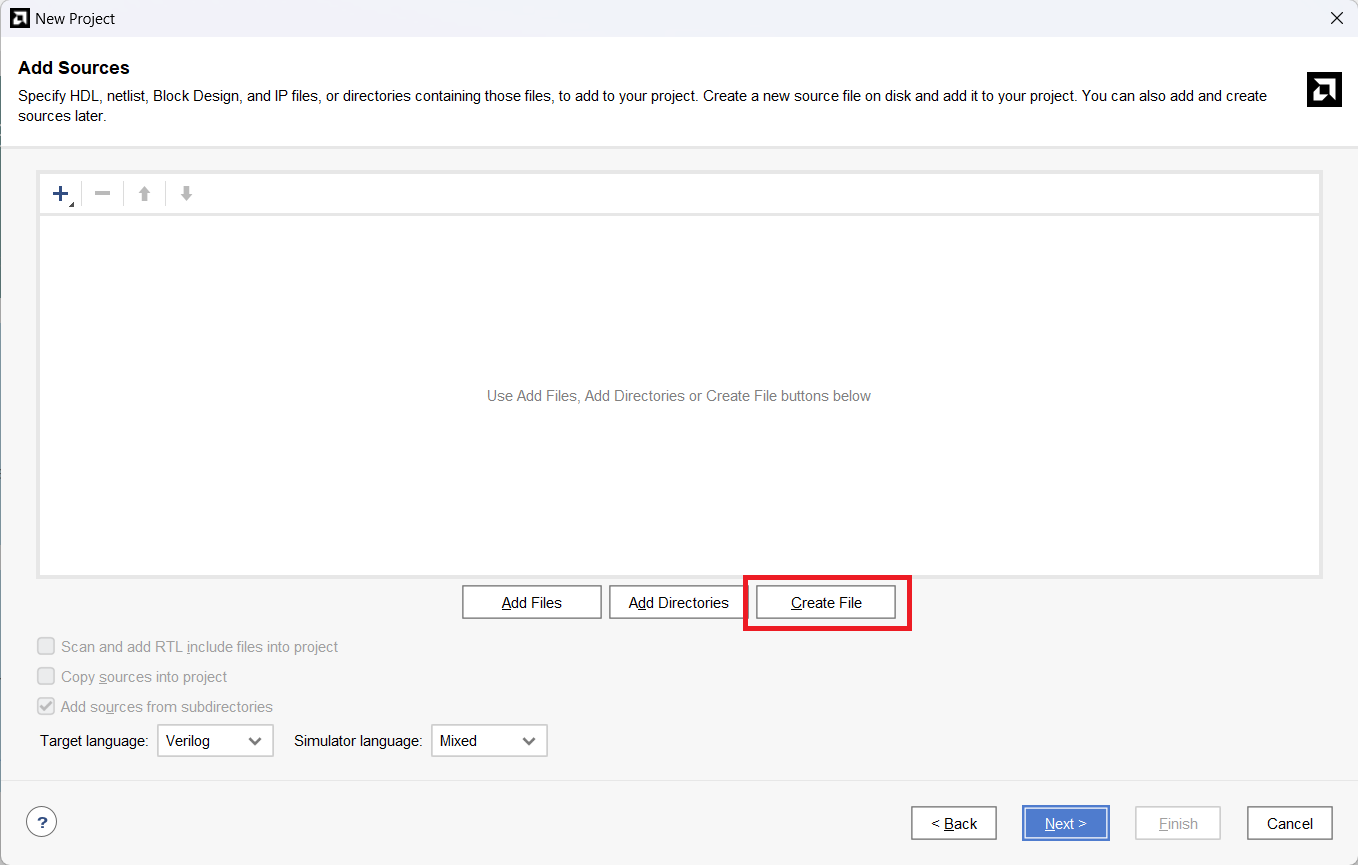

Add Sourcesの画面で「Create File」をクリックする。

Add Sources その1 -

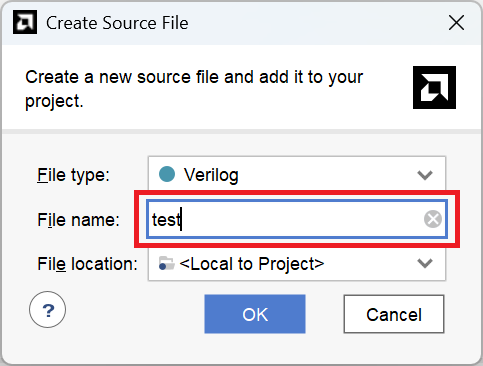

ファイル名を以下の通りに設定して「OK」をクリックする。

- File name:test

Add Sources その2 -

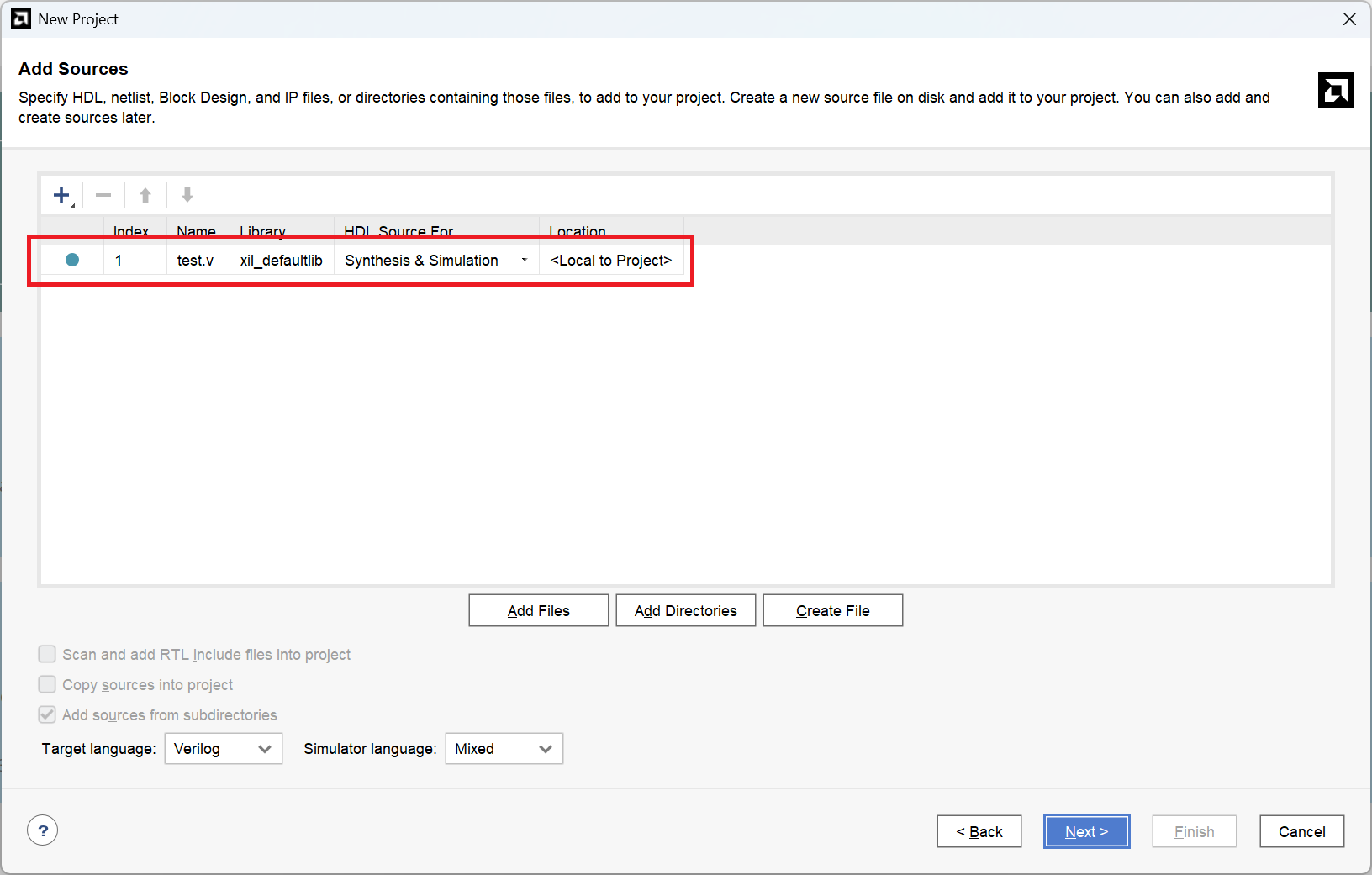

Add Sourcesの画面で作成したファイルが追加されていることを確認し、「Next」をクリックする。

Add Sources その3 -

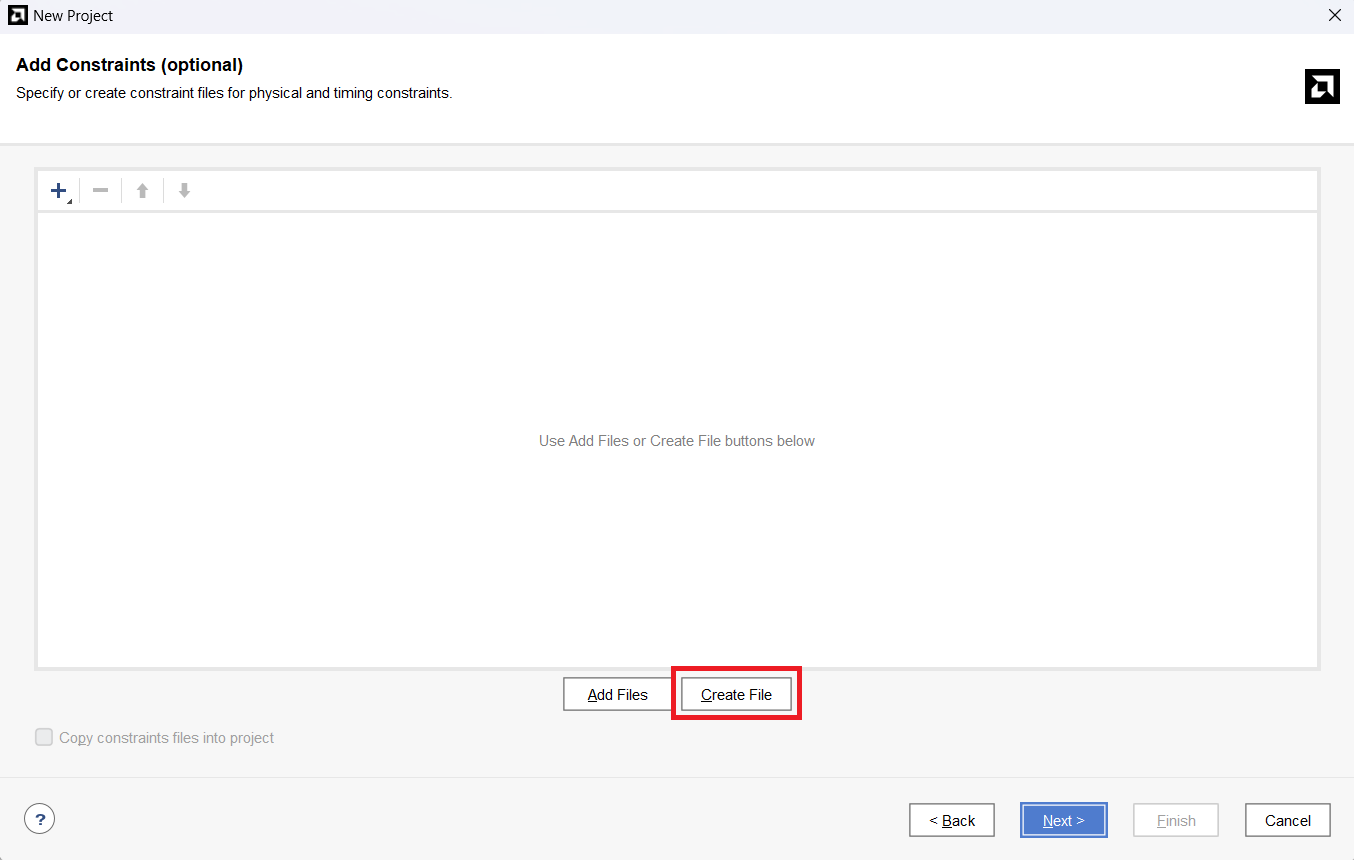

Add Constraints (optional)の画面で「Create File」をクリックする

Add Sources その4 -

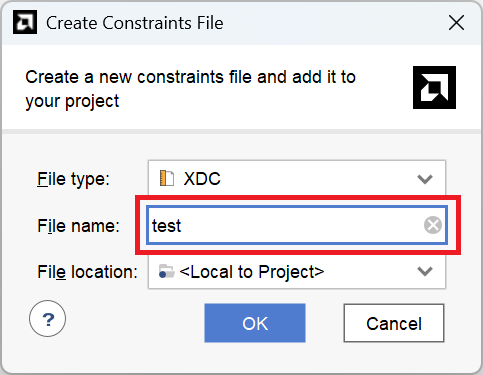

ファイル名を設定して「OK」をクリックする。

File name:test

Add Sources その5 -

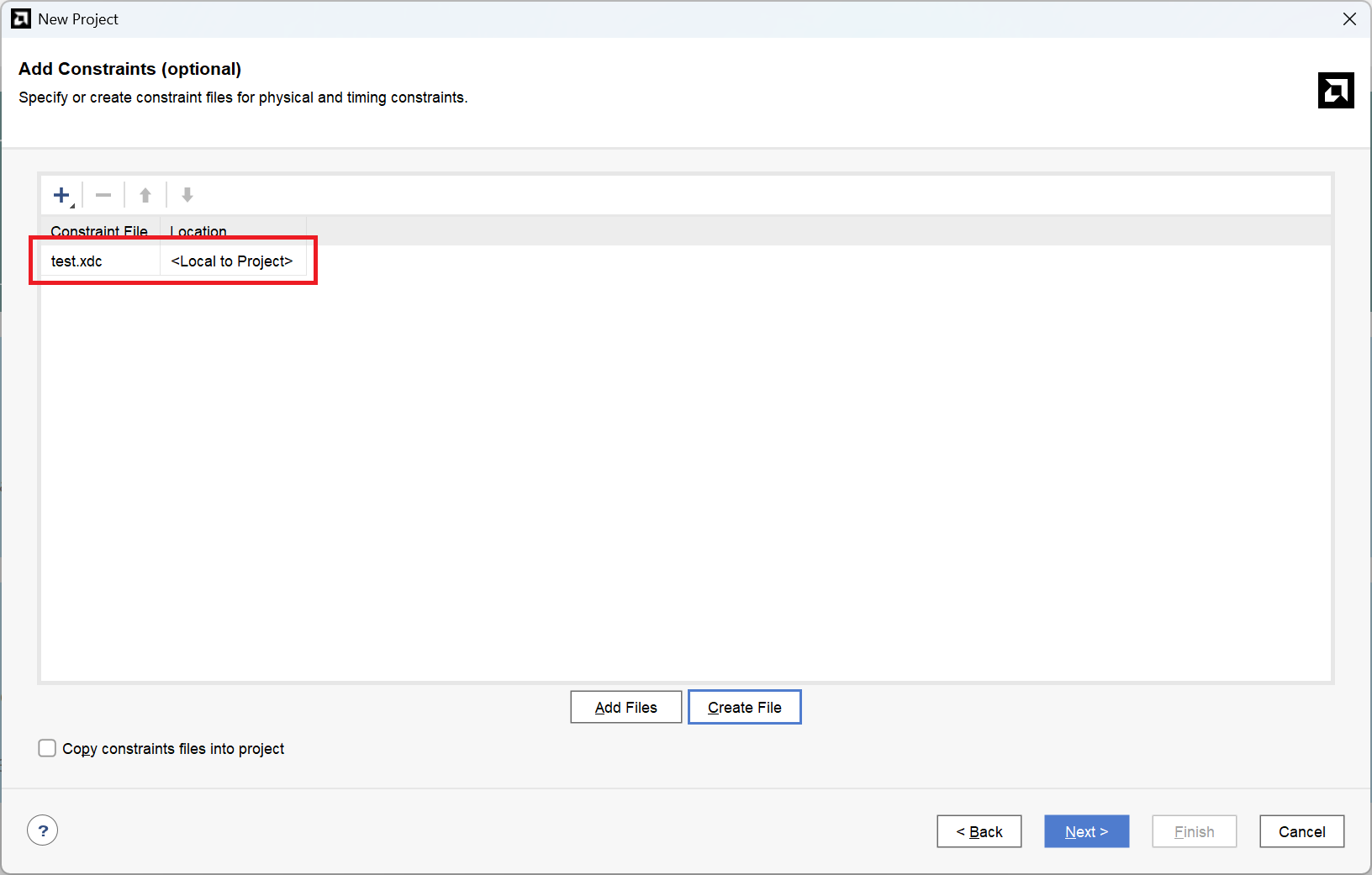

Add Constraints (optional)の画面で作成したファイルが追加されていることを確認し、「Next」をクリックする。

Add Sources その6 -

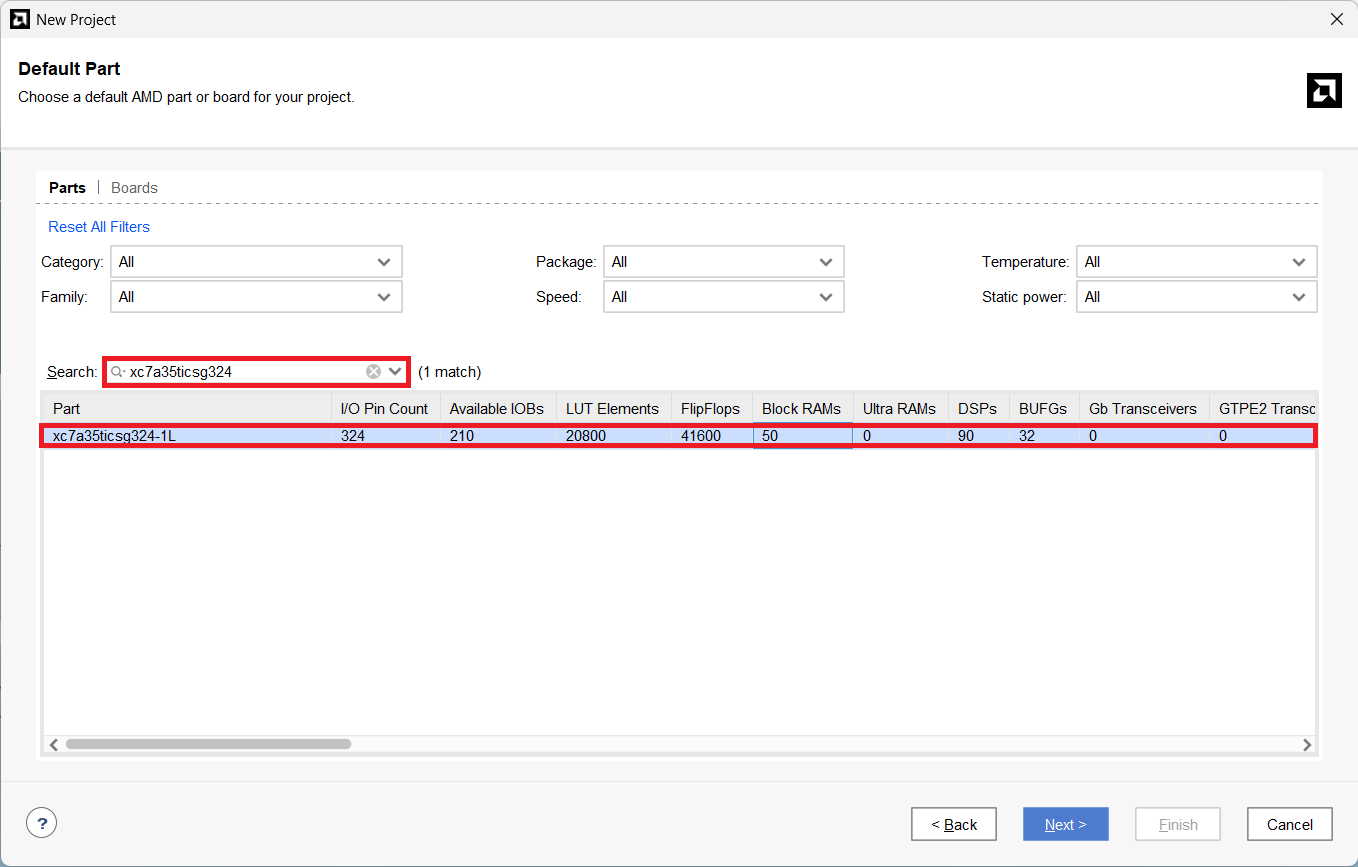

Default Partの画面で「Parts」を開き、「Search」で「xc7a35ticsg324」と検索する。

「xc7a35ticsg324-1L」を選択し、「Next」をクリックする。

Add Sources その7 -

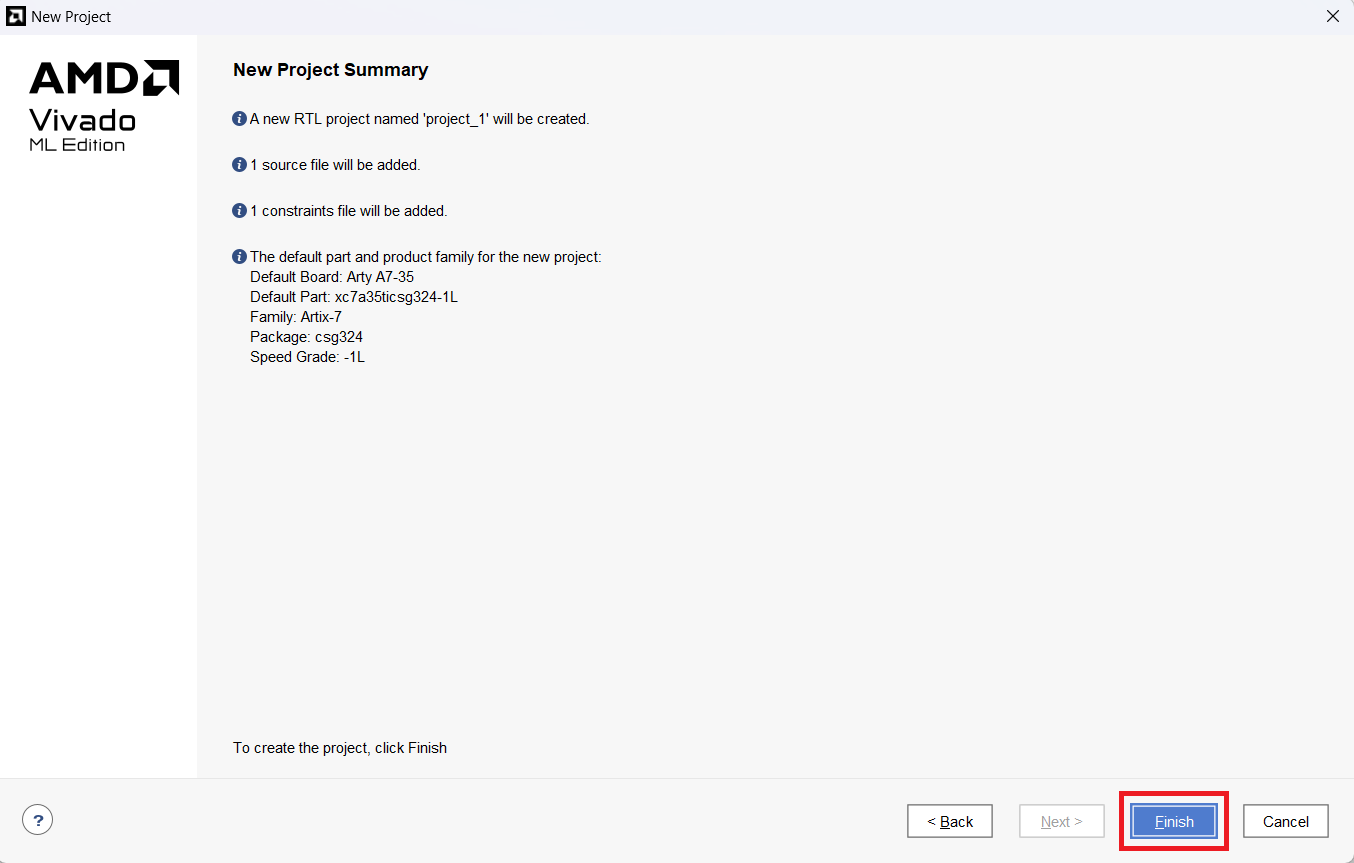

New Project Summaryの画面で「Finish」をクリックする。

Add Sources その9 -

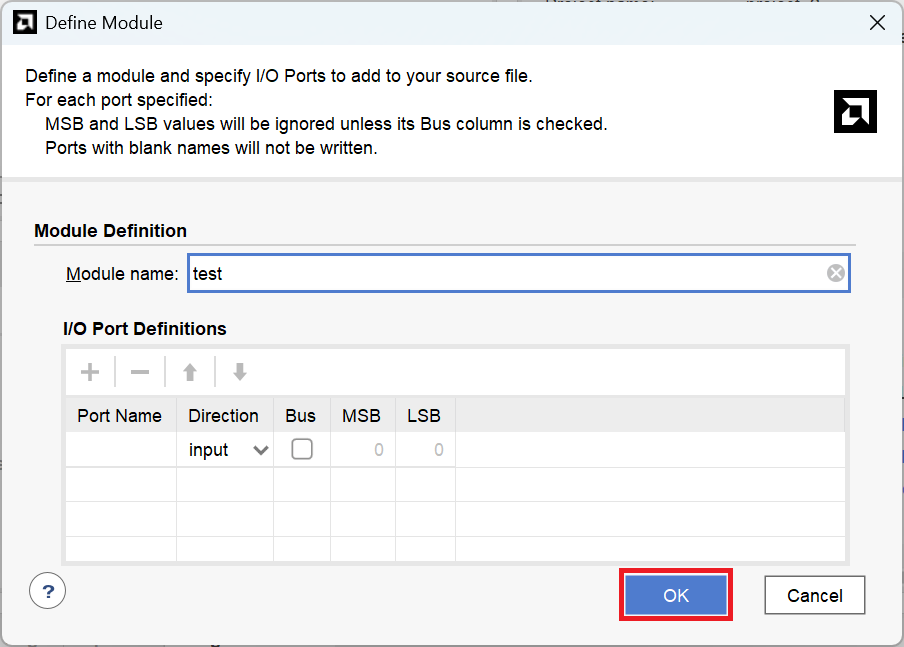

「OK」をクリックする。

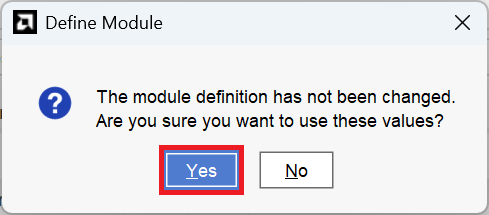

Define Module その1 「Yes」をクリックする。

Define Module その2 -

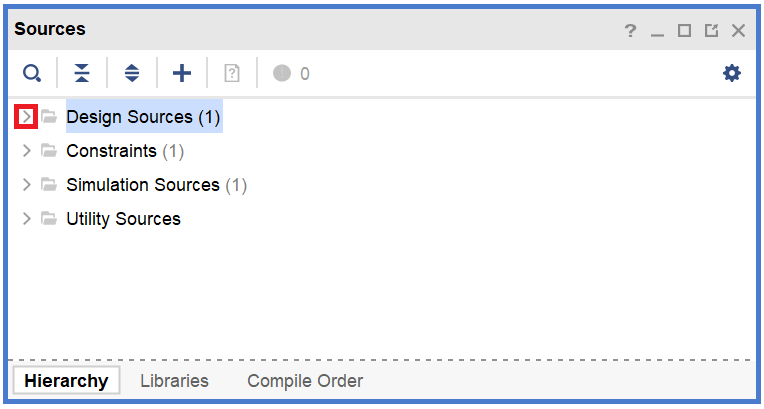

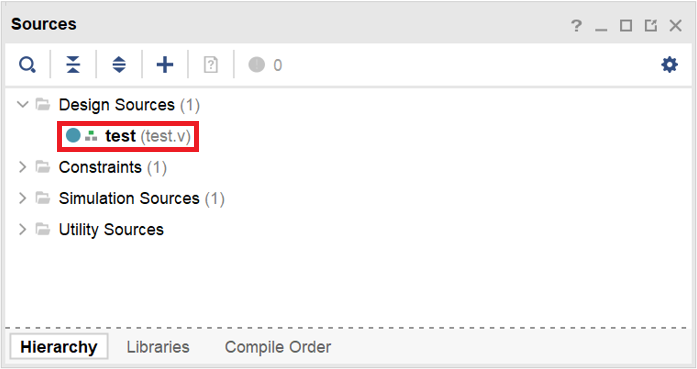

「Sources」の赤枠で囲まれた部分をクリックし、「Design Sources」を展開する。

Design Sources 「test.v」をクリックする。

test.v 実験書 p.151のリスト1を入力し、保存(Ctrl + S)する。

リスト1はWebclass上にも掲載してある。

-

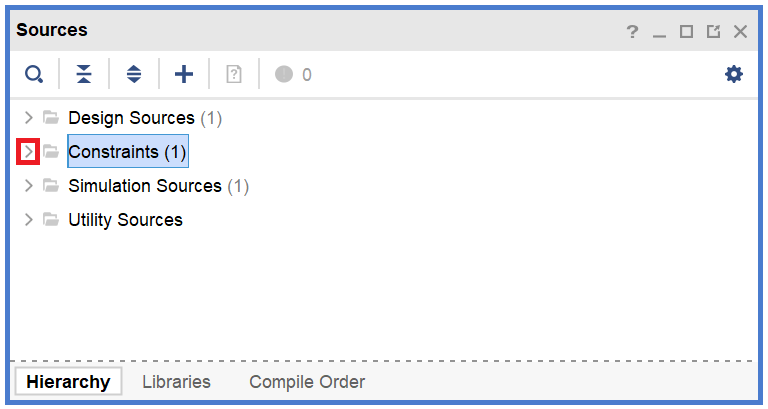

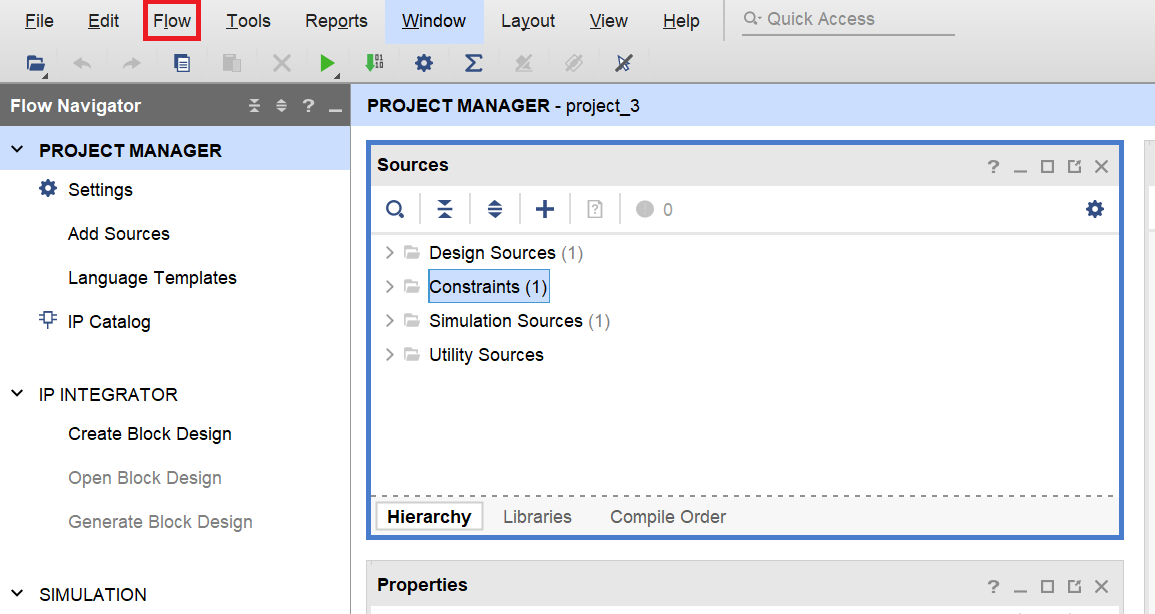

「Sources」の赤枠で囲まれた部分をクリックし、「Constraints」を展開する。

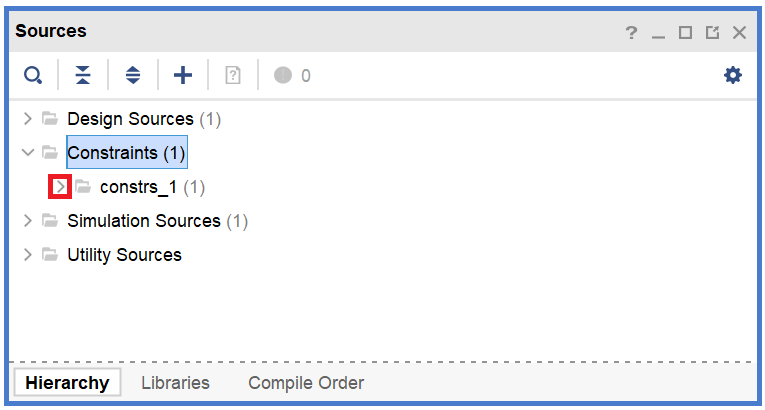

Constraints 「Constraints」の赤枠で囲まれた部分をクリックし、「constrs_1」を展開する。

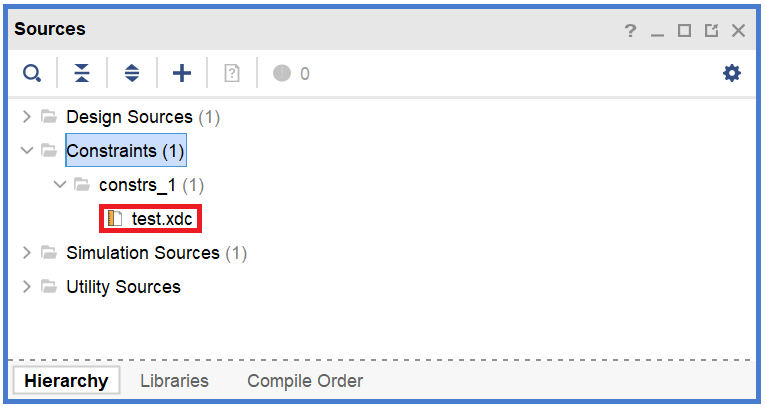

constrs_1 「test.xdc」をクリックする。

test.xdc 実験書 p.151のリスト2を入力し、保存(Ctrl + S)する。

リスト2はWebclass上にも掲載してある。

-

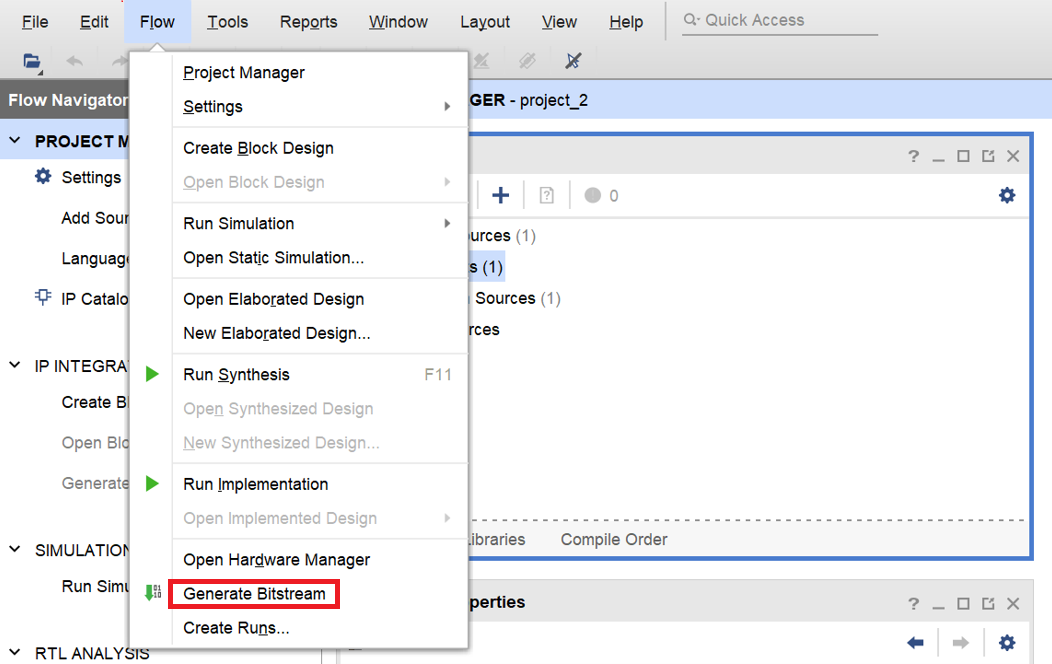

「Flow」をクリックする。

Flow 「Generate Bitstream」をクリックする。

Generate Bitstream -

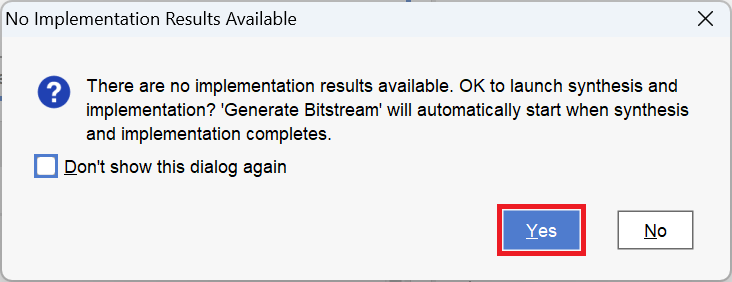

「Yes」をクリックする。

No Implementation -

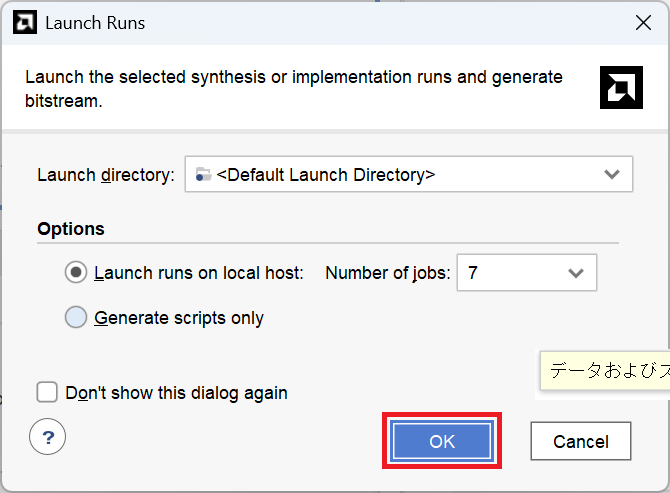

「OK」をクリックする。

Launch Runs -

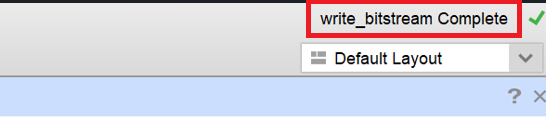

「Running synth_design」→「Initializing Design」→「Running opt_design」→「Running route_design」→「Running write_bitstream」→「Write_bitstream complete」の順番で右上に表示される。

または、左側のFlow NavigatorよりPROJECT MANAGERクリック、下側Design Runsタブ クリックで進行状況を確認できる。

Write_bitstream complete -

「Open Hardware Manager」を選択し、「OK」をクリックする。

Bitstream Generation Completed -

続きは実験室で行う。